# Using Linear Programming Techniques for Scheduling-based Random Test-case Generation

Amir Nahir Yossi Shiloach Avi Ziv

# Agenda

- What is Scheduling-based Test-case Generation

- CSP Model

- Mixed Integer Linear Problems (MIP)

- MIP Model

- Results

- Future Directions

- Combining CSP & MIP

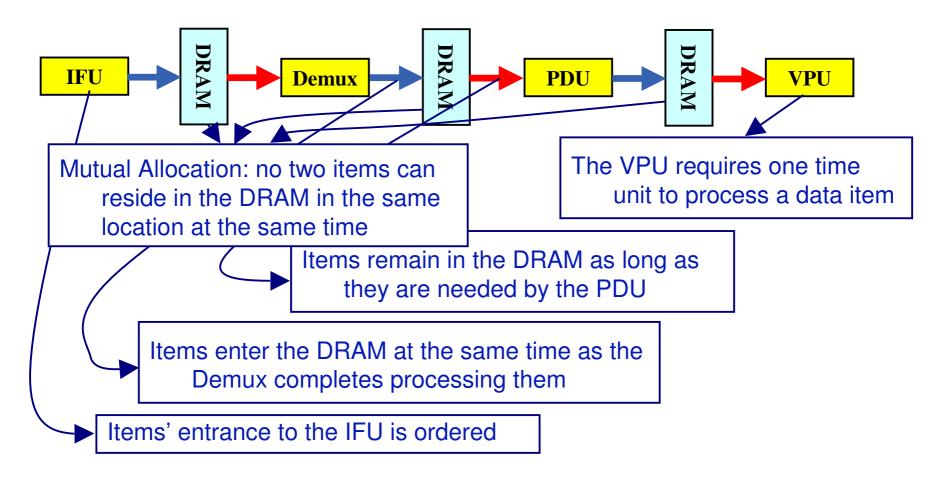

Scheduling-based Test-case Generation – DVD Player SoC

Example I/O 700.00.00. **MMU** ports **DVD Drive Input Unit IPBB** (IFU) To TV **Video Processing Unit MPEG2 Video** (VPU) Decoder (PDU) **Demultiplexer Audio Processing** Unit (APU) RISC CPU -Controller **IBBP**

# Constructing a scheduling problem

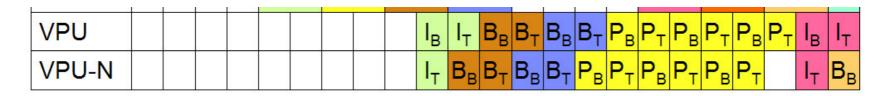

# **Scheduling Solution**

|       | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10             | 11             | 12             | 13             | 14    | 15             | 16    | 17             | 18    | 19             | 20             | 21      | 22             | 23             |

|-------|---|---|---|---|---|---|---|---|---|----------------|----------------|----------------|----------------|-------|----------------|-------|----------------|-------|----------------|----------------|---------|----------------|----------------|

| IFU   |   |   | F | ) | E | 3 | E | 3 |   |                |                |                |                |       | F              | )     | E              | 3     | E              | 3              |         |                |                |

| Demux |   |   |   |   | F | ) | E | 3 | E | 3              |                |                |                |       |                |       | F              | )     | E              | 3              | E       | 3              |                |

| PDU   |   |   |   |   |   |   | F | ) | E | 3              | E              | 3              |                |       |                |       |                |       | F              | )              | E       | 3              | В              |

| VPU   |   |   |   |   |   |   |   |   |   | <b>I</b> B     | I <sub>T</sub> | $B_B$          | B <sub>T</sub> | $B_B$ | B <sub>T</sub> | $P_B$ | $P_{T}$        | $P_B$ | $P_{T}$        | P <sub>B</sub> | $P_{T}$ | <b>I</b> B     | I <sub>T</sub> |

| VPU-N |   |   |   |   |   |   |   |   |   | I <sub>T</sub> | $B_B$          | B <sub>T</sub> | $B_B$          | $B_T$ | $P_B$          | $P_T$ | P <sub>B</sub> | $P_T$ | P <sub>B</sub> | $P_{T}$        |         | I <sub>T</sub> | $B_B$          |

# Scheduling Rules

#### Basic rules:

- Duration of processing

- Order within the processing core

- Order between processing cores

#### More Complex rules:

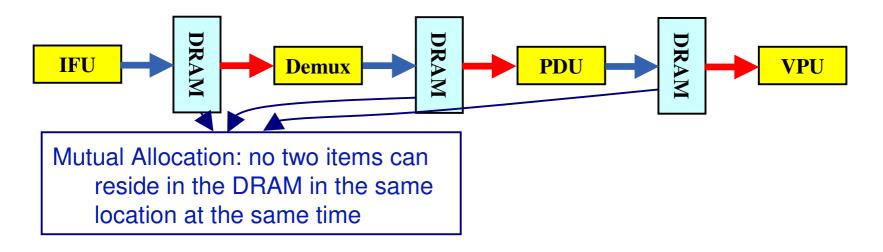

- Mutual exclusion: two items cannot be processed by the same core at the same time

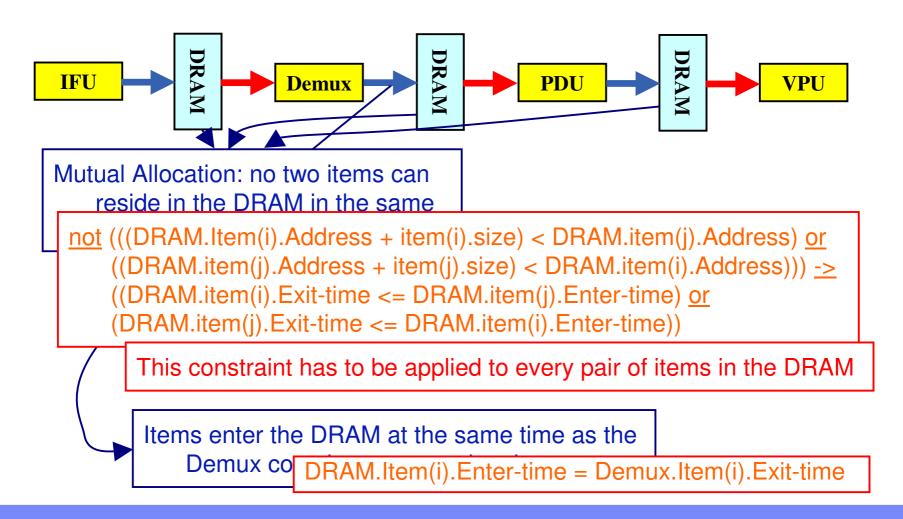

- Mutual allocation: two items cannot be stored in the same location at the same time

# Scheduling Rules (cont.)

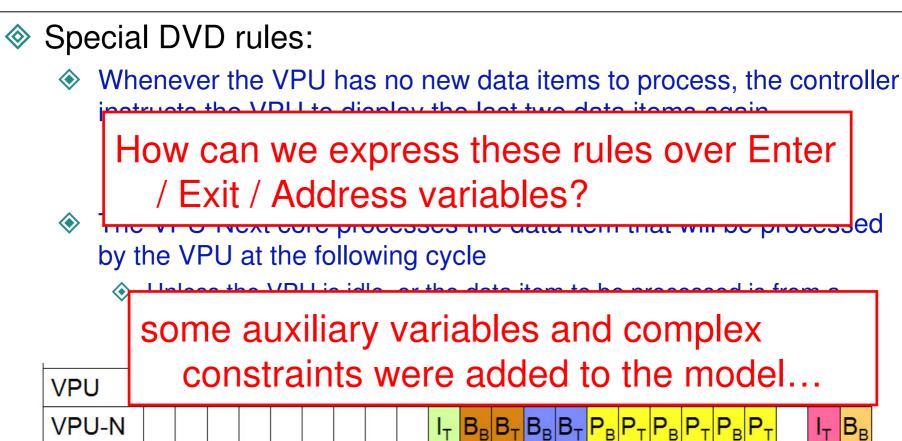

#### Special DVD rules:

- Whenever the VPU has no new data items to process, the controller instructs the VPU to display the last two data items again

- Causing the image on the viewer's screen to freeze

- The VPU-Next core processes the data item that will be processed by the VPU at the following cycle

- Unless the VPU is idle, or the data item to be processed is from a different group. In these cases, VPU-Next should be idle

#### Constraint Satisfaction Problems - Definition

[ Mackworth, Freuder, Montanari, Dechter, Rossi, ...]

- ♦ CSP P = {V, D, C}

- Variables

- Address, register\_value

- Domains (finite sets) for each variable

- Address: 0x0000 0xFFFF

- Number of bytes in a 'load': { 1, 2, 4, 8, 16 }

- Constraints (relations) over variables

- ♦ (load n bytes) → (align address to n bytes boundary)

- value(base\_reg) + displacement = address

- Solution for a CSP

- Every variable is assigned a value from its domain, such that all constraints are satisfied

- ♦ All solutions are born equal. There is no better or best solution!

# Modeling our scheduling problem using CSP

#### [Based on a well-known Scheduling->CSP reduction]

- Variables

- <core , data-item, enter-time / exit-time / address>

- ♦ IFU.I-Frame.Enter-time

- DRAM.B-Frame.Exit-time

- DRAM.B-Frame.Address

#### Domains

- For enter/exit variables discrete time (clock cycles)

- ♦ For address variables DRAM addresses

#### **CSP Constraints**

# Modeling our scheduling problem using CSP – the harder cases...

# Mixed Integer Linear Problems - Definition

- $\Diamond$  MIP P = {V,R,C,f}

- Variables

- Ranges

- Upper bound & Lower bound

- - Constrain certain variables to receive integer values only

- A linear objective function

# Mixed Integer Linear Problems – Definition (cont.)

- Feasible solution for a MIP

- Every variable is assigned a value from its range, such that all constraints are satisfied

- Optimal solution for a MIP

- A feasible solution, such that there exists no other solution with lower value to the objective function

- MIP Solvers find optimal solutions

# Modeling our scheduling problem using MIP

#### Ranges

- **♦** Only [0,1]

- Decision Problems

#### Variables

♦ For each <core , data-item>:

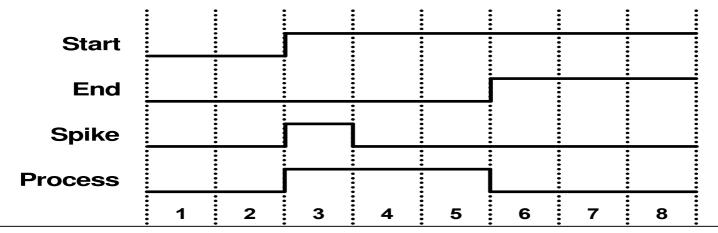

# Constructing the MIP "functions"

Not all variables are constrained to integers (but all variables will eventually be assigned with integer values)

#### **MIP Constraints**

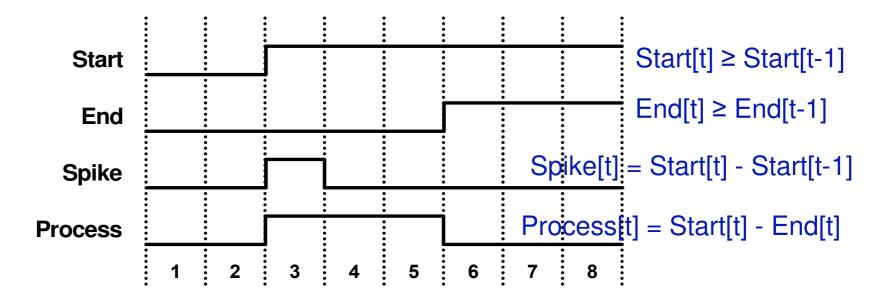

Item i's Start[t] ≥ Item (i+1)'s Start[t]

### MIP Constraints (cont.)

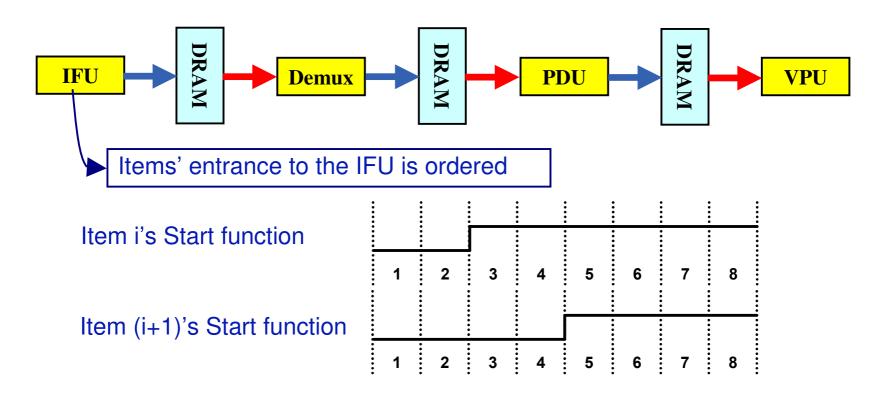

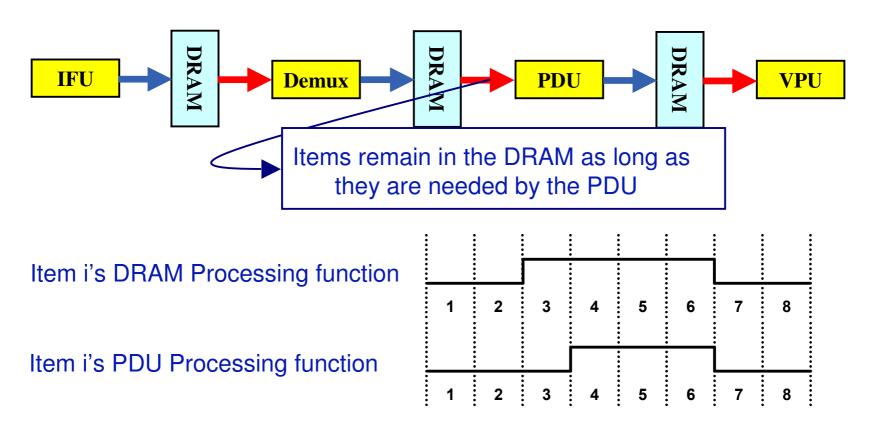

Item i's DRAM Start[t] = Item i's Demux End[t]

#### MIP Constraints (cont.)

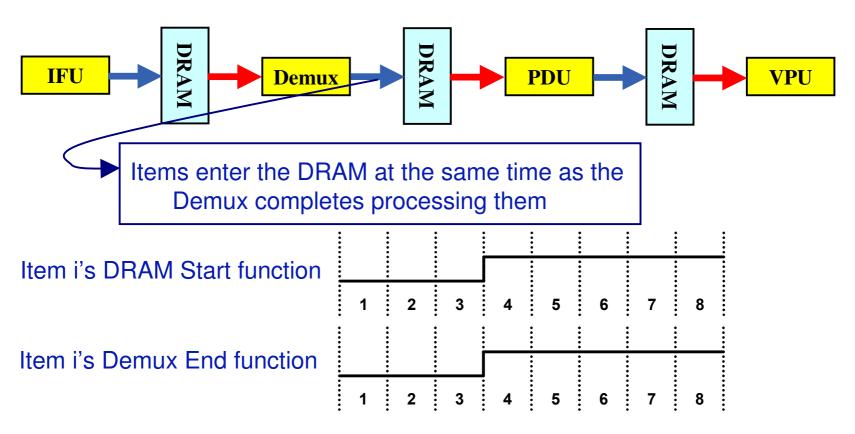

Item i's DRAM Processing[t] ≥ Item i's PDU Processing[t]

#### MIP Constraints (cont.)

Sum(Item i's size x Item i's DRAM Processing[t]) ≤ DRAM size

# Modeling our scheduling problem using MIP – the harder cases...

- Special DVD rt Remember these?

- ♦ Whenever the VPU has no new data items to process, the controller instruc  $\sum Process_{j}[t] \geq \sum Process_{j}[t-1]$  again  $\Rightarrow$  Ca  $j \in VPU$   $j \in VPU$

- The VPU-Next core processes the data item that will be processed

#### MIP & Randomness

- Test-case generators are required to generate many different solutions from the same test specification

- ♦ MIP solvers are optimizers they seek the optimal solution

- Our solution: we randomly select a set of variables and add them to the objective function

- In every execution, the solver is driven towards a different solution

#### **Experimental Results**

| Test name        | Framework | Variables | Constraints | Success<br>Rate | Time to Success |  |

|------------------|-----------|-----------|-------------|-----------------|-----------------|--|

| Play(IPBB,18)    | CSP       | 552       | 3077        | 100%            | 40.76           |  |

|                  | MIP       | 9412      | 14429       | 100%            | 1.73            |  |

| Play(IPBB,23)    | CSP       | 582       | 3260        | 90%             | 129.42          |  |

|                  | MIP       | 12002     | 18469       | 100%            | 18.99           |  |

| Play(IPBBPBB,28) | CSP       | 945       | 7562        | 90%             | 529.99          |  |

|                  | MIP       | 25410     | 39225       | 100%            | 90.75           |  |

| Play(IPBBPBB,33) | CSP       | 975       | 7795        | 40%             | 2181.20         |  |

|                  | MIP       | 29920     | 46265       | 100%            | 400.08          |  |

- An in-house solver was used for the CSP framework

- ♦ ILOG's CPLEX 10.0 was used for the MIP framework

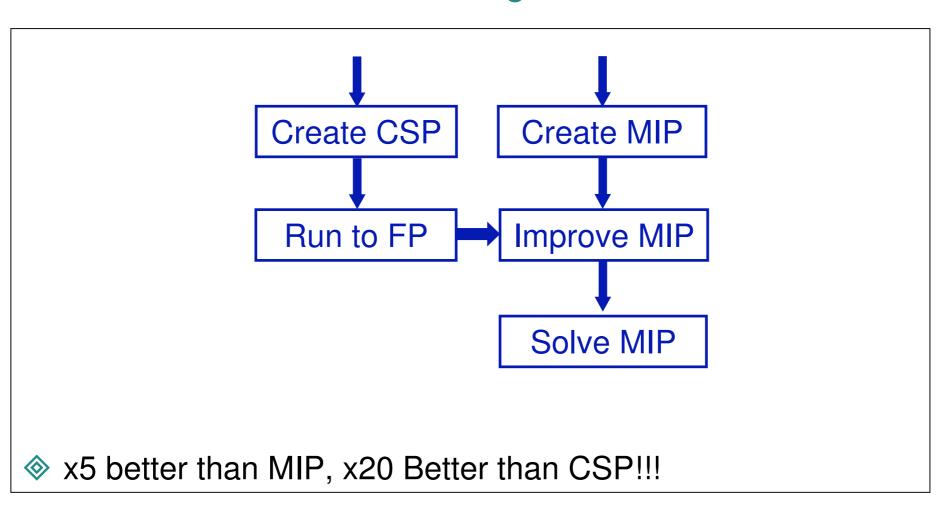

### Future Directions - Combining CSP & MIP

### Summary

- CSP is the prominent framework for test-case generation, and for good reasons

- Expressiveness

- Embedded randomness

- MIP is more efficient than CSP

- Because of its strong mathematical foundations

- MIP can't replace CSP, but can assist it in difficult problems

- By replacing CSP over specific problems

- Through hybrid technologies

#### **Questions Please**